Lab Introduction

現今IC產業蓬勃,隨著電晶體尺寸的縮小,單一晶片上可容納的電晶體數目也隨之增加,增加速率基本上遵循摩爾定律(Moore's Law),以每18~24個月成長一倍增加中。傳統人工設計方式無法跟上電晶體數量的快速成長,單一晶片上十萬、百萬,甚至到如今的一億、十億個電晶體已經變成了設計者的巨大挑戰。

為了因應傳統人工無法解決的大數量級問題,電子設計自動化(EDA - Electronic Design Automation)漸漸被發展成一門學問。工程師及學者設計演算法與軟體,並利用電腦進行運算以得出所期望的結果,從而完成設計。

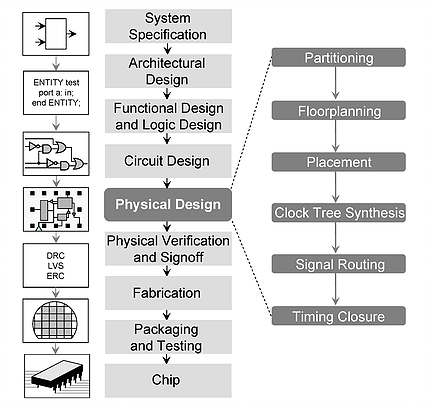

IC設計流程可分為前端(Front-end)與後端(Back-end),前端決定IC的功能、結構,組成的元件...等,僅關乎設計本身而不論在晶片上會產生的影響,故又被稱為邏輯設計(Logic design);後端則根據前端的結果,並且根據元件間的連線、功率...等性質,來決定各元件在晶片上的位置、導線的行經路徑與粗細...等,所有實際在晶片上需要解決的問題,因而又被稱為實體設計(Physical design)。

VLSI的Design Flow如右圖所示,而本實驗室的研究領域著重於整個Flow中的Physical Design這部分。